河北铭泰震安减隔震器材有限公司

联系人:张经理

手机:18732871219

邮箱:18632878593@163.com

地址:河北省衡水市高新技术开发区

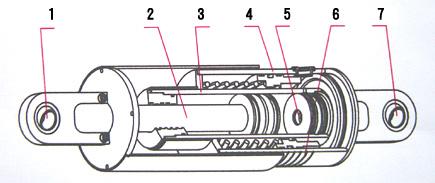

阻尼器原理

日期:2020-10-19 点击量:

在CPU的设计中,一般输出线的直流负载才能够驱动一个TTL负载,而在连接中,CPU的一根地址线或数据线,或许连接多个存储器芯片,但存储器芯片都为MOS电路,主要是电容负载,直流负载远小于TTL负载。故小型体系中,CPU可与存储器直接相连,在大型体系中就需求加阻尼器。

任何程序或数据要为CPU所运用,要先放到主存储器(内存)中,即CPU只与主存交换数据,所以主存的速度在很大程度上决议了体系的工作速度。程序在工作期间,在一个较短的时间距离内,由程序发生的地址往往会集在存储器的一个很小规划的地址空间内。指令地址原本就是连续分布的,再加上循环程序段和子程序段要多次重复履行,因而对这些地址中的内容的访问就自然的具有时间会集分布的倾向。

数据分布的会集倾向不如程序这么明显,但对数组的存储和访问以及工作单元的挑选能够使存储器地址相对地会集。这种对部分规划的存储器地址一再访问,而对此规划外的地址访问甚少的现象被称为程序访问的部分化(LocalityofReference)性质。

由此性质可知,在这个部分规划内被访问的信息集结随时间的改变是很缓慢的,如果把在一段时间内一定地址规划被一再访问的信息集结成批地从主存中读到一个能高速存取的小容量存储器中寄存起来,供程序在这段时间内随时选用而减少或不再去访问速度较慢的主存,就能够加快程序的工作速度。

这个介于CPU和主存之间的高速小容量存储器就称之为高速阻尼存储器,简称Cache。不难看出,程序访问的部分化性质是Cache得以完成的原理基础。同理,构造磁盘高速阻尼存储器(简称磁盘Cache),也将进步体系的整体工作速度CPU一般设有一级缓存(L1Cache)和二级缓存(L2Cache)。

一级缓存是由CPU制造商直接做在CPU内部的,其速度极快,但容量较小,一般只需十几K。PⅡ以前的PC一般都是将二级缓存做在主板上,并且能够人为晋级,其容量从256KB到1MB不等,而PⅡCPU则选用了全新的封装方法,把CPU内核与二级缓存一起封装在一只金属盒内,并且不能够晋级。二级缓存一般比一级缓存大一个数量级以上,另外,在CPU中,现已出现了带有三级缓存的情况。

- 2020-10-19阻尼器原理

- 2020-10-17阻尼器只是一个构件

- 2020-10-16阻尼器应用于马桶盖

- 2020-09-21阻尼器适用范围

- 2025-04-16钢结构阻尼器安装办法